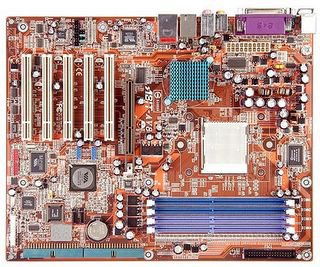

Nominally called the IDE (Integrated Drive Electronics) bus; how ever it's more correctly known as the ATA (Advanced Technology Attachment) specification [ATA Bus]. The IDE bus is used in Personal Computers [PCs] as a hard-drive or peripheral bus to interconnect the PC mother board and a hard drive. The IDE bus is a Parallel bus. With the introduction of the Serial ATA [SATA] specification Parallel ATA [IDE] is now being called PATA.

The specification has been up-graded a number of times each building on the past specification. ATA-1 and 2 were single documents, but like SCSI, after ATA-2 the specification was divided into a number of different documents. Most maintain backward compatibility, keeping in mind the cable changed. Each new version of the standard saw an increase in bus speed. The data transfer rate is shown after each version listed below. The current maximum IDE bus speed is 133MBytes/sec [133MBps].

Data is passed Single-Ended,via data line and ground. Only the 40 pin connector pin out are referenced below, which are used on 3.5-inch drives, but there is also a 50 pin connector used on 2.5-inch drives. The 50 pin connector adds the power and Master/Slave functions. PCMCIA uses a 68 pin connector. A graph showing the difference between ATA and Ultra ATA timing is shown on the below. The standard defines a single Host or adaptor which connects to one [device 0] or two [device 1] devices in a daisy chained configuration. The IDE, ATA connector pinout is listed in the table below. Note; there is text to decode the 80 pin cable onto the 40-pin connector.. There are a number of versions of the ATA bus, with each of the different versions listed below. The Serial ATA: which replaced the ATA bus is listed on its own page. Details for each bus version are listed below. A graphic which provides a comparison of all the different IDE interfaces listed here is provided on the HardDrive Interface Speed page.

ATA-1 (IDE), [Obsolete] 8.3MBytes/sec, 8 or 16 bit data width, 40 pin data ribbon cable/connector. With a maximum of 2 devices on the bus. Using PIO Modes 0, 1 or 2. Performed no bus error correction. The ATA-1 specification was released in 1994, and was withdrawn in 1999.

ATA-2 (EIDE, or Fast ATA), [Obsolete] 16.6MBytes/sec, 8 or 16 bit data width, 40 pin data ribbon cable/connector. With a maximum of 4 devices on the bus. Using PIO Modes 0, 1, 2, 3, or 4. The ATA-2 specification was released in 1995 and was withdrawn in 2001.

ATA-3, 16MBytes/sec, 16 bit data width, 40 pin data ribbon cable/connector. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 1 and 2. Runs with 120nS Strobes (rising edge to rising edge). Includes CRC.

ATAPI (ATA Packet Interface)is the CD-ROM side of the interface. It uses the same connector as ATA, and adds 1 for analog and 1 for digital audio. The ATA-3 specification was released in 1997 and was withdrawn in 2002.

ATA-4 Ultra-ATA/33, 33MBytes/sec, 16 bit data width, 40 pin data ribbon cable/connector. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 1 and 2 and Ultra DMA modes 0, 1, and 2. Runs with 120nS Strobes (rising edge to rising edge), but used both edges of the Strobe producing an effective 60nS Strobe rate. 33MBps Transfer speed = [(1/120nS) x 2 bytes x 2]. Where 120nS cycle time is 4 clock periods at 30nS each. Added CRC checking. The ATA-4 standard was released in 1998.

ATA-5 Ultra-ATA/66, 66MBytes/sec, 16 bit data width 40 pin data connector/80 pin cable, with the additional 40 new pins being Ground. The new cable allows ATA/66 to run at a faster rate then ATA/33. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 1 and 2 and Ultra DMA modes 0, 1, 2, 3 and 4. Runs with 60nS Strobes (rising edge to rising edge), but uses both edges of the Strobe producing an effective 30nS Strobe rate. 66MBps Transfer speed = [(1/60nS) x 2 bytes x 2]. Where 60nS cycle time is 2 clock periods at 30nS each. The ATA-5 standard was released in 2000.

ATA-6 Ultra-ATA/100, 100MBytes/sec,16 bit data width 40 pin data connector/80 pin cable, with the additional 40 new pins being Ground. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 1 and 2 and Ultra DMA modes 0, 1, 2, 3, 4 and 5. 100MBps Transfer speed = [(1/40nS) x 2 bytes x 2]. Where 40nS cycle time is 2 clock periods at 20nS each. The ATA-6 standard was released in 2002.

ATA-7 Ultra-ATA/133, 133MBytes/sec,16 bit data width 40 pin data connector/80 pin cable, with the additional 40 new pins being Ground. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 0, 1 and 2 and Ultra DMA modes 0, 1, 2, 3, 4, 5 and 6. 133MBps Transfer speed = [(1/30nS) x 2 bytes x 2]. Where 30nS cycle time is 2 clock periods at 15nS each. The ATA-7 standard was released in 2005. With the introduction of Serial ATA, this is the last expected update of the IDE [PATA] bus. SATA: is faster, and requires a smaller cable, which means better air flow in the Chassis.

Serial ATA: (Ver 1.0) High Speed Serialized AT Attachment

Serial version of the IDE [ATA] spec. Uses a 4 conductor cable with two differential pairs [Tx/Rx], plus an additional three grounds pins and a separate power pin. Data runs at 150MBps [1.5GHz] using 8B/10B encoding and 250mV signal swings. Serial ATA is not compatible with the IDE [Parallel ATA] because the connectors are different, the voltage levels are different, and data format is different [SATA sends a bit at a time while PATA sends 16 bits at once]. SATA will not interface with the IDE bus. No cable can be made to connect SATA with IDE. However a converter may be purchased which translates SATA to PATA. One module appears as a 2" x 2" board, for $50 and converts IDE controllers 66/100/133/150 MB/s to Serial ATA 150.

Regardless of the electrical interface the drives uses, there are also Solid State Drives available that do not require a platter. Or just Hybrid Hard Disk Drives that still use a platter, but have a greater amount of Flash Memory.